数据存储架构与技术:第二章

存储介质

- 机械部分(主轴电机,盘片,磁头组等)+电子部分(主控,电机驱动芯片,传感器芯片,Flash/DRAM)

- 磁盘通过旋转(seek)和旋转(rotation)两个机械操作以扇区(sector)为单位额读写数据

- 磁盘访问延迟受限于寻道时间(seek time),旋转时间(rotation time),数据传输时间(data transfer time); 另外与磁盘利用率(为当前读写请求数量与磁盘最大吞吐率的比值)也有关。

- 磁盘向操作系统到处一个线性一维空间(LBA),磁盘内部通常以CHS描述扇区的PBA,CHS为Cylinder#,Head#,Sector#, 理论上由算术运算即可建立LBA/PBA之间的映射关系。实际上地址映射还应用了分区(Zone),重映射(Remap),偏移(skew)等技术

- 磁盘缓存包括写缓冲和读缓存(及预取), 写缓冲能提升写性能但掉电可能丢数据。

- 组件包括主控,闪存,固件,电源,连接器,DRAM,备电电容等

- 主控前端提供SATA,SAS,PCIe/NVME接口,后端提供多通道挂接闪存。 固件管理整盘资源,前端按协议与主机交互,内部FTL通过地址映射,垃圾回收,磨损均衡等模块管理闪存,另外还实施ECC,温度监控和电压监控;

- SSD对闪存的访问有多个级别的并发以实现高带宽

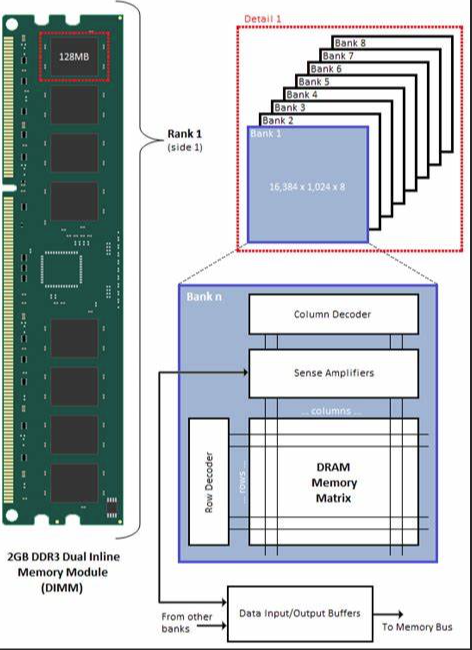

- DRAM地址拓扑:Channel -->DIMM -->RANK -->CHIP -->BANK -->Row & Column;

2. 一个CHIP内有多个BANK,这些BANK 共享控制线,地址线和数据线;单个CHIP的数据位宽为4bit/8bit/16bit, 同Rank内多个CHIP同时读写就可实现更大的位宽,在RANK内的不同CHIP共享地址线和控制线(而数据线不同)

3. DIMM包含一个或多个RANK;上图DIMM正反两面各有8个CHIP,分别组成一个RANK(正反各一个RANK)

4. DDR数据带宽与总线频率和位宽相关

5. DRAM读完成后需要从行缓存中将数据再次卸任原来的DRAM 行,此操作成为Pre-charage, 以此保留原有的数据。此外,DRAM 还需定期刷新以对抗Retention; 刷新有集中式刷新(每隔一定时间停止外部IO来让内存控制器对内存逐一刷新)和分布式刷新(对内存所有行交替进行刷新操作和外部读写操作)

- PCM:

- RRAM

- MRAM

- 光存储 CD/DVD/BD

- 磁带